×

随着现代电子技术、计算机技术的发展,各种总线应运而生。微型计算机的体系结构也发生了显著变化,如cpu运行速度的提高,多处理器结构的出现,高速缓冲存储器的广泛应用等,都要求有高速的总线来传输数据,从而出现了多总线结构。在多总线结构中,pci总线以其速度高、可靠性强、成本低及兼容性好等性能,在各种总线标准中占主导地位。

pci总线是一种兼容性最强、功能最全的计算机总线。他可同时支持多组外围设备,且不受制于处理器,为cpu及高速外围设备提供高性能、高吞吐量、低延迟的数据通路。pci支持5 v及3.3 v的通信环境,以反射波作为通信基础。当入射信号从无终端方向反射回来之后,反射波经过结构性干扰与入射波合成一体,完成电压与电流的驱动任务,因此pci又称“非终端式传输总线”。概括起来,pci总线有如下主要特点:

(1)在全部读写传送中可实现突发传送。

(2)并行总线操作。

(3)隐式仲裁。

(4)访问速度快。

(5)软件透明。

(6)自动配置。

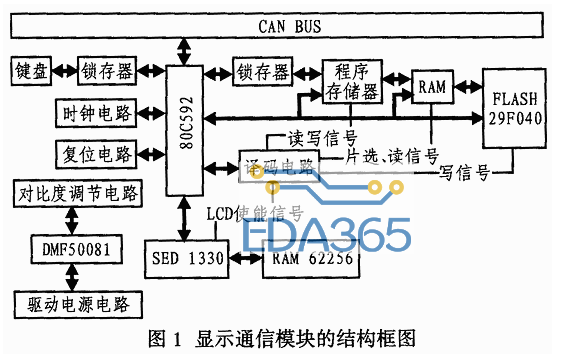

pci是一种高性能32/64 b地址数据复用总线,他在高度集成的外围控制器件、外围插件板和处理器/存储器之间作为互连机构应用。pci总线不仅可以应用到低档至高档的台式系统上,而且也可应用在便携式机及至服务器的范围中。在一个pci系统中,可做到高速外部设备和低速外部设备共享,pci总线与isa/eisa总线并存,其系统结构如图1所示[1]。

在一个pci应用系统中,取得了总线控制权的设备称为“主设备”,而被主设备选中以进行通信的设备称为“从设备”或“目标设备”。相应的接口信号线,通常分为必备的和可选的2大类。若只作为目标设备,至少需要47条接口信号线,若作为主设备,则需要49条。利用这些信号线可处理数据、地址,实现接口控制、仲裁及系统功能。面向主设备与目标设备综合考虑,并按功能分组将这些信号表示。

总线命令用来规定主、从设备之间的传输类型,他出现于地址期的c/be[3∶0]#线上。当一个主设备获得pci总线的拥有权时,他可启动表1[2]的任何一种交易类型。在一个交易的地址期c/be[3∶0]#用于表明交易命令和类型。

pci总线对协议、时序、负载、电气特性及机械特性等技术指标均有严格的规定和要求。下面简要介绍pci总线的基本操作规则(或协议)[1]:

(1)基本的总线传输机制:一次突发传输包括一个地址期和一个或若干个数据期。

(2)除rst#,inta#~intd#之外的所有信号都是在时钟的上升沿被采样。

(3)pci总线上数据传输基本上都由frame#,irdy#和trdy#三条信号线控制。

(4)当frame#和irdy#都无效时,接口处于空闲状态。frame#信号建立后的第一个时钟前沿是地址期,在这个时钟前沿上传送地址和总线命令;下一个时钟前沿开始一个或若干个数据期。irdy#和trdy#有效的时钟前沿进行一次数据传输。

(5)无论是主设备还是目标设备,一旦承诺了数据传输,就要进行到本次传输完成。

(6)frame#撤销而irdy#建立,表示主设备准备好了最后一次数据传输,等到目标设备发出了trdy#信号,就标志着最后一次传输的完成。

pci总线配置空间的目的是提供一个合适的配置设备的集合,使其满足当前和未来系统配置特性的需要。配置空间是一个容量为256 b并具有特定记录结构的地址空间。该空间分为头标区和设备相关区2部分。一个设备的配置空间不仅在系统自举时可以访问,而是在其他任何时间内也是可以访问的。软件必须使用i/o,通过进行内存的存取来访问设备配置空间[2]。

头标区的各个字段用来惟一地识别设备,并使设备能以一般方法控制。头标区有64 b,分为2部分:前16 b的定义对任意类型的设备都相同,剩下的48 b则随各设备支持的功能有所不同,其结构如图3所示[2]。

基于pci总线的设备,都必须在头标区内提供制造商id、设备id、谬令和状态。其他寄存器的设置则可根据设备的功能进行选择(如做为保留寄存器)。

任何因设备而异的寄存器都不在这个头标区,而必须安排在64~255所对应的地址空间。所有多字节的数据字段中某些为将来使用而保留地位,软件必须小心正确地处理他们。在读取时,软件必须以适当的屏蔽来抽取定义过的位,而进行写操作时,软件必须保证在保留位的值不发生变化。

『本文转载自网络,64体育的版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多